|

MT2523 API Reference

LinkIt SDK v4

|

|

MT2523 API Reference

LinkIt SDK v4

|

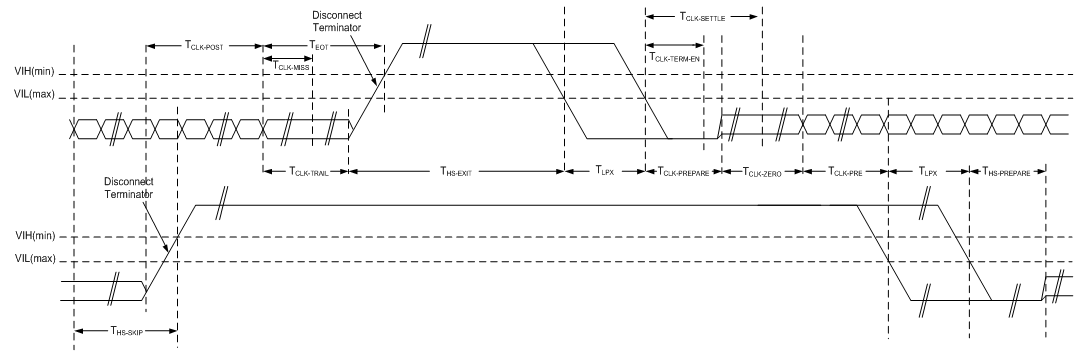

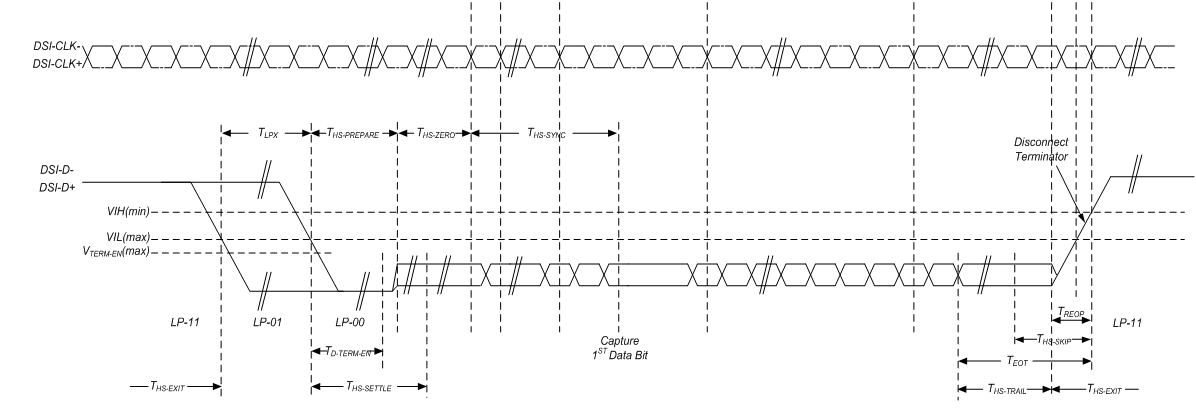

This event structure presents the DSI D-PHY timing setting structure, as shown below. More...

#include <hal_display_dsi.h>

Data Fields | |

| uint32_t | da_hs_trail |

| Time that the transmitter drives the flipped differential state after last payload data bit of HS transmission burst. More... | |

| uint32_t | da_hs_zero |

| Time that the transmitter drives the HS-0 state prior to transmitting the Sync sequence. More... | |

| uint32_t | da_hs_prep |

| Time that the transmitter drives the Data Lane LP-00 Line state immediately before the HS-0 Line state starts the HS transmission. More... | |

| uint32_t | lpx |

| Transmitted length of any Low-Power state period to display module. More... | |

| uint32_t | da_hs_exit |

| Time that the transmitter drives LP-11 following an HS burst. More... | |

| uint32_t | ta_get |

| Time that the MCU drives the Bridge state (LP-00) after accepting control during a Link Turnaround. More... | |

| uint32_t | ta_sure |

| Time that the MCU waits after the LP-10 state before transmitting the Bridge state (LP-00) during a Link Turnaround. More... | |

| uint32_t | ta_go |

| Time that the display module drives the Bridge state (LP-00) before releasing control during a Link Turnaround. More... | |

| uint32_t | clk_hs_trail |

| Time that the transmitter drives the HS-0 state after the last payload clock bit of HS transmission burst. More... | |

| uint32_t | clk_hs_zero |

| Time that the transmitter drives the HS-0 state prior to starting the Clock. More... | |

| uint32_t | clk_hs_post |

| Time that the transmitter continues to send HS clock after the last associated Data Lane has transitioned to LP Mode. More... | |

| uint32_t | clk_hs_prep |

| Time that the HS clock shall be driven by the transmitter prior to any associated Data Lane beginning the transition from LP to HS mode. More... | |

This event structure presents the DSI D-PHY timing setting structure, as shown below.

| uint32_t clk_hs_post |

Time that the transmitter continues to send HS clock after the last associated Data Lane has transitioned to LP Mode.

| uint32_t clk_hs_prep |

Time that the HS clock shall be driven by the transmitter prior to any associated Data Lane beginning the transition from LP to HS mode.

| uint32_t clk_hs_trail |

Time that the transmitter drives the HS-0 state after the last payload clock bit of HS transmission burst.

| uint32_t clk_hs_zero |

Time that the transmitter drives the HS-0 state prior to starting the Clock.

| uint32_t da_hs_exit |

Time that the transmitter drives LP-11 following an HS burst.

| uint32_t da_hs_prep |

Time that the transmitter drives the Data Lane LP-00 Line state immediately before the HS-0 Line state starts the HS transmission.

| uint32_t da_hs_trail |

Time that the transmitter drives the flipped differential state after last payload data bit of HS transmission burst.

| uint32_t da_hs_zero |

Time that the transmitter drives the HS-0 state prior to transmitting the Sync sequence.

| uint32_t lpx |

Transmitted length of any Low-Power state period to display module.

| uint32_t ta_get |

Time that the MCU drives the Bridge state (LP-00) after accepting control during a Link Turnaround.

| uint32_t ta_go |

Time that the display module drives the Bridge state (LP-00) before releasing control during a Link Turnaround.

| uint32_t ta_sure |

Time that the MCU waits after the LP-10 state before transmitting the Bridge state (LP-00) during a Link Turnaround.